XRF Webinar

In this webinar we introduce X-ray Fluorescence Spectroscopy (XRF) which is a analytical technique used for elemental analysis of materials.

Home » Package to Die: An Extraction Overview

Packaging serves as an intermediate link in the semiconductor manufacturing process, beginning with the wafer fabrication of numerous integrated circuits (ICs) and culminating in the final encapsulation of the finished product. While ICs can be packaged in various forms, all share the common goal of protecting the circuits from environmental factors and enabling their integration into larger assemblies. Many packaging types utilize lead frames or substrates where diced chips are bonded with adhesives and electrically connected via bonding wires or solder bumps. To safeguard them, the bonded ICs are encapsulated by an epoxy molding compound (EMC). This encapsulation is essential for shielding the ICs from external factors such as environmental stressors.

Sample preparation is not confined to a single technique but rather serves as an umbrella term encompassing a wide range of methods used to facilitate different objectives such as fault isolation, ATE testing, repackaging and electrical probing. Depending on the specific goals of the preparation, the complexity and intricacy of these methods can vary. One of those more involved processes is to fully extract ICs from various package types.

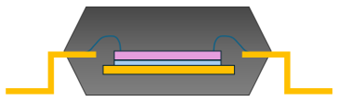

Wire bonded packaging has been a cornerstone of the electronics industry since its inception. While advanced packaging methods have gained traction, wire bonding remains widely used for assembling many semiconductor packages today. Its versatility, cost efficiency and well-established manufacturing processes make it a reliable choice for chips that do not require ultra-high interconnect densities, ensuring its relevance for years to come. In this packaging type, dies are mounted onto a die paddle using die attach materials, with bond wires welded to bond pads along the die’s perimeter and connected to lead fingers or the lead frame.

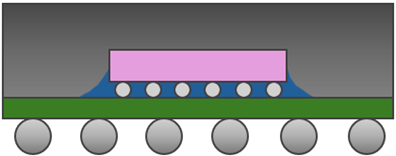

Flip chip, on the other hand, packaging has gained significant popularity due to its numerous advantages in the semiconductor industry. The introduction of the redistribution layer (RDL) revolutionized traditional electrical connection configurations by enabling bond pad pin redistribution. RDL technology forms a metal layer on the active side of the chip, allowing pins to be reassigned to virtually any position on the die surface. This innovation enables die pads, traditionally located along the die perimeter for wire bonding, to be reorganized anywhere on the chip. To extract dies from such packages, the sample undergoes mechanical polishing until the mold compound is thinned, and the interconnects have been removed. This is typically followed by a quick chemical etching step to remove any residual mold compound from the circuitry and bond pads.

Extraction methodologies can generally be distilled into two primary steps: mechanical polishing and chemical etching. While this framework provides a simplified overview, the actual complexity of the process varies significantly based on the type of package being analyzed. For example, the extraction of a standard wire-bonded single-die package is often relatively straightforward. The bond wires serve as reference points to guide the polishing process through the mold compound and towards the die surface.

However, as package architecture becomes more intricate, the extraction process correspondingly increases in difficulty. Flip chip packages exemplify this complexity, as the sequence of die assembly plays a critical role in determining the appropriate extraction procedure. If the RDL is formed below the passivation layer, the entire IC sample can be chemically etched briefly to remove the residual mold compound, leaving the die intact. Conversely, when the RDL is positioned above the passivation layer, exposing the bump side to chemicals could risk damaging active circuitry. In such cases, a safer alternative involves selectively decapsulating the backside silicon and carefully removing the underfill material along the sidewalls of the die while preserving the die integrity.

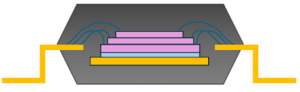

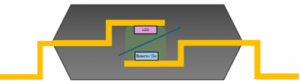

Beyond flip chips, other non-traditional packages—including but not limited to multilayer stacked dies, FETs with copper clips, optocouplers, and ceramic-mounted dies—can present additional challenges. Copper clip die extraction requires that the clip and underlying solder attach be thinned as far as possible before chemical exposure. If both interfaces remain too thick, extended chemical exposure times may inadvertently etch into underlying structures and compromise the integrity of the package. In all cases, the success and quality of extractions depend heavily on the practitioner’s experience to detect subtle visual or structural cues that indicate proximity to the die surface while maintaining planarity throughout the procedure.

As a third-party lab, EAG frequently encounters a wide range of packaging technologies across different industries. With assemblies becoming more complex, incorporating technologies like multi-chip modules and 3D packaging, the need for precise extraction has grown significantly. This experience has enabled us to refine methodologies for successful die extractions from various package types.

EAG’s continuous mission is to tackle new challenges, create solutions, and deliver the most effective support for our clients’ failure analysis investigations. Contact us to learn more.

In this webinar we introduce X-ray Fluorescence Spectroscopy (XRF) which is a analytical technique used for elemental analysis of materials.

October 23

During this live Ask the Expert event, we will answer pre-submitted questions from our audience regarding brazing.

Automated Test Equipment (ATE) systems are carefully designed to test a wide range of semiconductor devices. EAG provides tailored ATE test solutions to meet the unique needs of clients.

GC-MS can help with failure analysis or contamination characterization analysis on 3D printed parts. Utilizing a variety of different sampling techniques, GC-MS is a versatile tool that can identify specific species of volatile organic compounds.

To enable certain features and improve your experience with us, this site stores cookies on your computer. Please click Continue to provide your authorization and permanently remove this message.

To find out more, please see our privacy policy.